# **PCI-1720U**

4-channel Isolated D/A Output Card with Universal PCI Bus

**User Manual**

## Copyright

This documentation and the software included with this product are copyrighted 2004 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice.

No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. Information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties which may result from its use.

#### Acknowledgments

PC-LabCard is a trademark of Advantech Co., Ltd. IBM and PC are trademarks of International Business Machines Corporation. MS-DOS and Windows are trademarks of Microsoft Corporation. Intel and Pentium are trademarks of Intel Corporation. All other product names or trademarks are properties of their respective owners.

Part No. 2003172010 1st Edition Printed in Taiwan March 2005

## **Product Warranty (2 years)**

Advantech warrants to you, the original purchaser, that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products which have been repaired or altered by persons other than repair personnel authorized by Advantech, or which have been subject to misuse, abuse, accident or improper installation. Advantech assumes no liability under the terms of this warranty as a consequence of such events.

Because of Advantech's high quality-control standards and rigorous testing, most of our customers never need to use our repair service. If an Advantech product is defective, it will be repaired or replaced at no charge during the warranty period. For out-of-warranty repairs, you will be billed according to the cost of replacement materials, service time and freight. Please consult your dealer for more details.

If you think you have a defective product, follow these steps:

- Collect all the information about the problem encountered. (For example, CPU speed, Advantech products used, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages you get when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

- 3. If your product is diagnosed as defective, obtain an RMA (return merchandize authorization) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a fully-completed Repair and Replacement Order Card and a photocopy proof of purchase date (such as your sales receipt) in a shippable container. A product returned without proof of the purchase date is not eligible for warranty service.

- 5. Write the RMA number visibly on the outside of the package and ship it prepaid to your dealer.

#### **CE Notification**

PCI-1720U has passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This kind of cable is available from Advantech. Please contact your local supplier for ordering information.

#### **Safety Precaution - Static Electricity**

Follow these simple precautions to protect yourself from harm and the products from damage.

- 1. To avoid electrical shock, always disconnect the power from your PC chassis before you work on it. Don't touch any components on the CPU card or other cards while the PC is on.

- 2. Disconnect power before making any configuration changes. The sudden rush of power as you connect a jumper or install a card may damage sensitive electronic components.

#### **Packing List**

Before setting up the system, check that the items listed below are included and in good condition. If any item does not accord with the table, please contact your dealer immediately.

1x PCI-1720U card

1x Companion CD-ROM (DLL driver included)

1x User Manual (this manual)

# Contents

| Chapter | 1 General Information                                    | 2     |

|---------|----------------------------------------------------------|-------|

| 1.1     | Introduction                                             | 2     |

| 1.2     | Features                                                 | 2     |

| 1.3     | Applications                                             | 3     |

| 1.4     | Specifications                                           | 3     |

| 1.5     | Block Diagram                                            | 4     |

| Chapter | 2 Installation                                           | 6     |

| 2.1     | Initial Inspection                                       | 6     |

| 2.2     | Unpacking                                                | 6     |

| 2.3     | Installation Instructions                                | 7     |

| Chapter | 3 Jumpers and I/O Connectors                             | 10    |

|         | Figure 3.1: PCI-1720U Jumper Locations                   | 10    |

| 3.1     | Jumper Settings                                          | 10    |

|         | 3.1.1 Using Jumpers to set Current Sink Ranges           | 10    |

|         | Figure 3.2: Jumper Settings for PCI-1720U's Current Sink |       |

|         | Range                                                    |       |

|         | 3.1.2 Jumper JP5 Setting for the Reset State             |       |

|         | Figure 3.3: Jumper JP5 Setting for the Reset State       |       |

| 3.2     | Connector and Pin Assignments                            |       |

|         | Figure 3.4: PCI-1720U Pin Assignments                    |       |

|         | 3.2.1 Signal Descriptions of I/O Connector               |       |

| 3.3     | 8 · · · · · · · · · · · · · · · · ·                      |       |

|         | Table 3.1: Board ID Setting (SW1)                        | 14    |

|         | 3.3.1 Identity Register                                  |       |

| Chapter | 4 Register Structure and Format                          | 18    |

| 4 1     | _                                                        |       |

|         | I/O Port Address Map                                     |       |

| 7.2     | Table 4.1: PCI-1720U Register Format and Function Des    | crip- |

|         | tion                                                     | 19    |

|         | 4.2.1 D/A Output Channel 0 to 3                          |       |

|         | Table 4.2: Register for D/A Data                         |       |

|         |                                                          | 0     |

|        | Table 4.3: Register for D/A Voltage Range and Polarity      |    |

|--------|-------------------------------------------------------------|----|

|        | Table 4.4: Output Range of D/A Channel n                    |    |

|        | 4.2.3 Synchronized Output Prompt Register                   |    |

|        | 4.2.4 Synchronized Output Control Bitt                      |    |

|        | Table 4.5: Synchronized Output Control Bit                  |    |

| 4      | 3 Unipolar and Bipolar Binary Code Tables                   | 22 |

|        | Table 4.6: Unipolar Binary Code Table                       | 22 |

|        | Table 4.7: Bipolar Binary Code Table                        | 22 |

| Chapte | r 5 Signal Connections                                      | 24 |

| 5.     | 1 Overview                                                  | 24 |

|        | 2 D/A Voltage Output Connections                            |    |

|        | Figure 5.1: Floating-load Conn. for D/A Voltage Output24    |    |

|        | Figure 5.2: Grounded-load Conn. for D/A Voltage Output      | 25 |

|        | Figure 5.3: Differential-load Conn. for D/A Voltage Output  | 25 |

| 5      | 3 Current Sink Connections                                  | 26 |

|        | Figure 5.4: Grounded-load conn. w/ a floating power supply  | 26 |

|        | Figure 5.5: Floating-load conn. w/ a grounded power supply  | 26 |

|        | Figure 5.6: Floating-load Conn. with an Internal +12 VDC Po | w- |

|        | er Supply                                                   | 27 |

| 5.4    | 4 Current Sink Load and Power Supply                        | 27 |

|        | Figure 5.7: PCI-1720U Current Sink Circuitry                | 27 |

| Append | lix A Calibration                                           | 30 |

|        | 1 Overview                                                  |    |

|        | Figure A.1: PCI-1720U VR assignment                         |    |

| A      | 2 Unipolar Output Calibration                               |    |

|        | 3 Bipolar Output Calibration                                |    |

|        |                                                             | 32 |

# **General Information**

## **Chapter 1 General Information**

## 1.1 Introduction

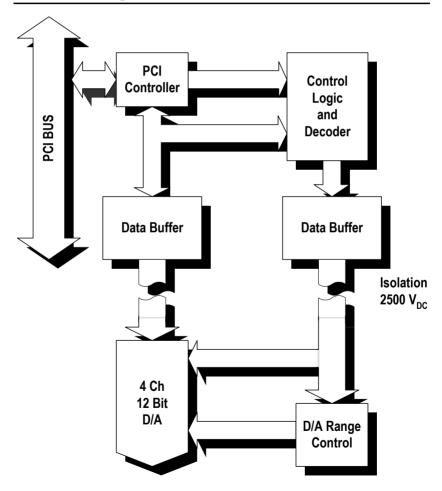

PCI-1720U is an isolated digital-to-analog output card for the Universal PCI bus. It provides four 12-bit analog output channels with isolation protection of 2,500 V DC between the outputs and the PCI bus. This is ideal for industrial applications where high-voltage protection is required.

## Keeping the Output Settings and Values after System Reset

The four outputs can be set independently to different ranges: 0 to  $\pm$ 5 V, 0 to  $\pm$ 10 V,  $\pm$ 5 V,  $\pm$ 10 V, 0 to 20 mA (sink) or 4 to 20 mA (sink). When the system is hot reset (the power is not shut off), PCI-1720U can either retain the last analog output settings and values, or return to its default configuration based on its jumper setting. This practical function eliminates danger caused by misoperation during unexpected system resets.

## **PCI-bus Plug & Play**

The PCI-1720U uses a PCI controller to interface the card to the PCI bus. The controller fully implements the PCI bus specification Rev 2.1. All bus relative configurations, such as base address and interrupt assignment, are automatically controlled by software.

## 1.2 Features

- Four 12-bit D/A output channels

- Multiple output ranges

- 2500  $V_{\mbox{\scriptsize DC}}$  isolation between the outputs and the PCI bus

- · Keeps the output settings and values after system reset

- One 37-pin D-type connector for easy wiring

- BoardID switch

- Universal PCI Bus

- Glitch-free power up

## 1.3 Applications

- · Process control

- Programmable voltage source

- Programmable current sink

- · Servo control

## 1.4 Specifications

#### D/A Output

• Channels: 4 isolated D/A channels

• **Resolution:** 12 bits

• Output Ranges: Unipolar:  $0 \sim +5 \text{ V}, 0 \sim +10 \text{ V}$

Bipolar:  $\pm 5 \text{ V}, \pm 10 \text{ V}$

Current loop (sink):  $0 \sim 20$  mA,  $4 \sim 20$  mA

• Throughput: 500 kHz

• Accuracy: ±0.024%

• Isolation Voltage: 2,500 V DC between the outputs and the PCI bus

• Output Current: ±5 mA max.

• Current Loop Excitation Voltage: 50 V max.

• On-board 12 V<sub>DC</sub> Excitation Voltage: (80 mA max.)

## **Power Consumption**

- +5 V @ 350 mA (typical), 500mA (Max.)

- +12V @ 200 mA (typical), 350mA (Max.)

## Physical

• Connector: 37-pin D-type connector

• **Dimensions:** 175 x 100 mm (6.9" x 3.9")

### **Environment**

- Operating Temperature:  $0 \sim 60^{\circ}$  C  $(32 \sim 140^{\circ}$  F)

- Storage Temperature:  $-20 \sim 70^{\circ}$  C ( $-4 \sim 158^{\circ}$  F)

- Operating Humidity: 5 ~ 95 % RH non-condensing (refer to IEC 68-2-3)

- MTBF: over 71,280 hrs @ 25° C, grounded, fixed environment

## 1.5 Block Diagram

# Installation

## **Chapter 2 Installation**

## 2.1 Initial Inspection

Before installing PCI-1720U, check the card for visible damage. The card has been carefully inspected both mechanically and electrically before shipment. It should be free of marks and in perfect order upon receipt.

As you unpack the PCI-1720U, check for signs of shipping damage (damaged box, scratches, dents, etc.). If it is damaged or fails to meet specifications, notify our service department or your local sales representative immediately. Also, call the carrier immediately and retain the shipping carton and packing materials for inspection by the carrier. We will then make arrangements to repair or replace the unit.

## 2.2 Unpacking

PCI-1720U contains components that are sensitive and vulnerable to static electricity. Discharge any static electricity on your body to ground by touching the back of the system unit (grounded metal) before you touch the board.

Remove the PCI-1720U card from its protective packaging by grasping the card's rear panel. Handle the card only by its edges to avoid static discharge which could damage its integrated circuits. Keep the antistatic package. Whenever you remove the card from the PC, protect the card by storing it in this package.

You should also avoid contact with materials that hold static electricity such as plastic, vinyl and styrofoam.

Check the product contents inside the packing. There should be one card, one CD-ROM, and this manual. Make sure nothing is missing.

## 2.3 Installation Instructions

The PCI-1720U can be installed in any PCI slot in the computer. However, refer to the computer user's manual to avoid any mistakes and danger before you follow the installation procedure below:

1. Turn off your computer and any accessories connected to the computer..

Warning! TURN OFF your computer power supply whenever you install or remove any card, or connect and disconnect cables.

- 2. Disconnect the power cord and any other cables from the back of the computer.

- 3. Remove the cover of the computer.

- 4. Select an empty PCI slot. Remove the screw that secures the expansion slot cover to the system unit. Save the screw to secure the interface card to the retaining bracket.

- 5. Carefully grasp the upper edge of the PCI-1720U. Align the hole in the retaining bracket with the hole on the expansion slot and align the gold striped edge connector with the expansion slot socket. Press the card into the socket gently but firmly. Make sure the card fits the slot tightly.

- 6. Secure the PCI-1720U by screwing the mounting bracket to the back panel of the computer.

- 7. Attach any accessories (37-pin D type cable, wiring terminal, etc.) to the card

- 8. Replace the cover of your computer. Connect the cables you removed in step 2.

- 9. Turn the computer on.

# Jumpers and I/O Connectors

## **Chapter 3 Jumpers and I/O Connectors**

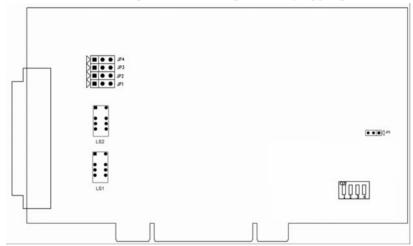

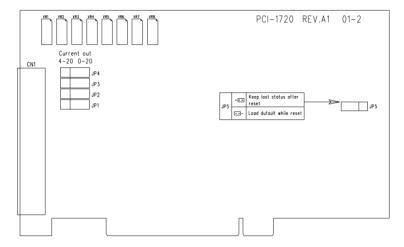

The PCI-1720U is a Plug & Play compatible card, i.e. the system BIOS assigns the system resources such as the base address and the interrupt number automatically. There are only 2 functions with 5 jumpers to configure to your applications requirements. The following sections offer the necessary information for setting the PCI-1720U's jumpers. You may need to refer to the figure below for help in identifying jumper locations.

Figure 3.1: PCI-1720U Jumper Locations

## 3.1 Jumper Settings

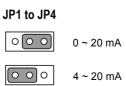

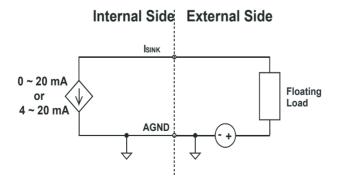

## 3.1.1 Using Jumpers to set Current Sink Ranges

Jumpers JP1 to JP4 are used to select each channel's current sink range, either 4  $\sim$  20 mA or 0  $\sim$  20 mA. Jumpers JP1 to JP4 correspond with D/A channel 0 to channel 3 respectively. In order to use the current sink range, you have to set the PCI-1720U output voltage range to 0  $\sim$  5 V. The figure below shows the correct jumper settings for the PCI-1720U's current sink range.

Figure 3.2: Jumper Settings for PCI-1720U's Current Sink Range

Note!

In order to maintain accurate outputs for your field applications, it is important that you calibrate the PCI-1720U's variable resistors (VRs) from time to time. Calibration instructions are provided in Appendix A.

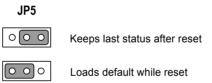

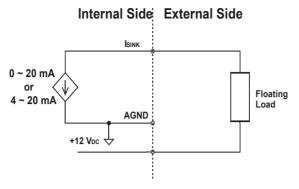

## 3.1.2 Jumper JP5 Setting for the Reset State

Jumper JP5 gives the PCI-1720U a new and valuable capability. With JP5 enabled, the PCI-1720U "memorizes" all D/A output settings and output values, and, in the event of a "hot" reset, i.e., the power is not shut off, the settings and output values present at each channel just prior to reset are still maintained. This feature is very useful for field applications. For example, it may allow a computer be "hot" reset without requiring the whole control system to shutdown. (Since output values are left unchanged.)

Complete loss of power to the card clears all settings and output values even if JP5 is enabled; i.e. if the power to the card is disconnected, the card's initial power-on state will be the default state. The default state is the output range for all channels is 0~5V and all the output values are 0V.

When jumper JP5 is disabled, power-off or "hot" reset results in outputs returning to their default state.

Figure 3.3: Jumper JP5 Setting for the Reset State

## 3.2 Connector and Pin Assignments

The PCI-1720U uses one DB-37 female connector, which is located on the card at CN1 (see Figure 3-1) and connects D/A signals to external devices. The following figure shows the pin assignments of the connector.

| NC       | 1   |    |     |

|----------|-----|----|-----|

| NO       | l ' | 20 | NC  |

| +12 Vout | 2   |    |     |

| AOND     |     | 21 | NC  |

| AGND     | 3   | 22 | NC  |

| AGND     | 4   |    |     |

|          | _   | 23 | NC  |

| Vout 0   | 5   | 24 | NC  |

| AGND     | 6   |    |     |

|          |     | 25 | NC  |

| Isink 0  | 7   | 26 | NC  |

| Vout 1   | 8   |    | 110 |

|          |     | 27 | NC  |

| AGND     | 9   | 28 | NC  |

| Isink 1  | 10  | 20 | 140 |

|          |     | 29 | NC  |

| Vout 2   | 11  | 30 | NC  |

| AGND     | 12  | 30 | NC  |

|          |     | 31 | NC  |

| Isink 2  | 13  |    | NO  |

| Vout 3   | 14  | 32 | NC  |

|          |     | 33 | NC  |

| AGND     | 15  |    |     |

| Isink 3  | 16  | 34 | NC  |

|          |     | 35 | NC  |

| NC       | 17  |    |     |

| NC       | 18  | 36 | NC  |

| 110      |     | 37 | NC  |

| NC       | 19  |    |     |

|          |     |    |     |

Figure 3.4: PCI-1720U Pin Assignments

## 3.2.1 Signal Descriptions of I/O Connector

| Signal Name | Reference | Direction | Description                                                                                                 |

|-------------|-----------|-----------|-------------------------------------------------------------------------------------------------------------|

| VOUT<03>    | AGND      | Output    | Analog Voltage Output Channels 0 through 3. These pins supply the voltage outputs for the analog outputs.   |

| ISINK<03>   | AGND      | Input     | Current Sink Channels 0<br>through 3.<br>These pins provide the<br>current loop sink input.                 |

| +12 V OUT   | AGND      | Output    | +12 VDC Source. This pin<br>is a +12 V DC power supply<br>(80mA max.) for current loop<br>exciting voltage. |

| AGND        | -         | -         | Analog Ground. The analog output voltage and +12 VDC source are referenced to these pins.                   |

| NC          | -         | -         | No Connection to pin                                                                                        |

## 3.3 Setting the BoardID Switch (SW1)

BoardID settings (0x20) are used to get the board's unique identifier. The PCI-1720U has a built-in DIP switch (SW1), which is used to define each card's unique identifier. You can determine the unique identifier in the register as shown in Table 3.2. When there are multiple identical cards in the same chassis, the BoardID switch helps differentiating the boards by identifying each card's device number with the switch setting. PCI-1720U's unique identifier has been set to 0 with the BoardID switch at the factory. If you need to adjust it to other numbers, set SW1 by referring to DIP switch setting.

| Table 3.1: Board ID Setting (SW1) |     |     |     |     |  |  |  |  |  |  |

|-----------------------------------|-----|-----|-----|-----|--|--|--|--|--|--|

| SW1                               | 3   | 2   | 1   | 0   |  |  |  |  |  |  |

| BoardID                           | ID3 | ID2 | ID1 | ID0 |  |  |  |  |  |  |

| 0 (default)                       | ON  | ON  | ON  | ON  |  |  |  |  |  |  |

| 1                                 | ON  | ON  | ON  | OFF |  |  |  |  |  |  |

| 2                                 | ON  | ON  | OFF | ON  |  |  |  |  |  |  |

| 3                                 | ON  | ON  | OFF | OFF |  |  |  |  |  |  |

| 4                                 | ON  | OFF | ON  | ON  |  |  |  |  |  |  |

| 5                                 | ON  | OFF | ON  | OFF |  |  |  |  |  |  |

| 6                                 | ON  | OFF | OFF | ON  |  |  |  |  |  |  |

| 7                                 | ON  | OFF | OFF | OFF |  |  |  |  |  |  |

| 8                                 | OFF | ON  | ON  | ON  |  |  |  |  |  |  |

| 9                                 | OFF | ON  | ON  | OFF |  |  |  |  |  |  |

| 10                                | OFF | ON  | OFF | ON  |  |  |  |  |  |  |

| 11                                | OFF | ON  | OFF | OFF |  |  |  |  |  |  |

| 12                                | OFF | OFF | ON  | ON  |  |  |  |  |  |  |

| 13                                | OFF | OFF | ON  | OFF |  |  |  |  |  |  |

| 14                                | OFF | OFF | OFF | ON  |  |  |  |  |  |  |

| 15                                | OFF | OFF | OFF | OFF |  |  |  |  |  |  |

## 3.3.1 Identity Register

You can determine the identity in the register as shown in the table below.

| Table 3.2: Identity Register of PCI-1720U |     |     |     |     |  |  |  |

|-------------------------------------------|-----|-----|-----|-----|--|--|--|

| Base+20                                   | 3   | 2   | 1   | 0   |  |  |  |

| Abbreviation                              | ID3 | ID2 | ID1 | ID0 |  |  |  |

## Note:

ID0: The least significant bit (LSB) of identifier

ID3: The most significant bit (MSB) of identifier

# Register Structure and Format

## **Chapter 4 Register Structure and Format**

## 4.1 Overview

PCI-1720U is delivered with an easy-to-use 32-bit DLL driver for user programming under Windows 98, 2000 and XP operating systems. We advise users to program the PCI-1720U using the 32-bit DLL driver provided by Advantech to avoid the complexity of low-level programming by register.

The most important consideration in programming the PCI-1720U card at register level is to understand the function of the card's registers. The information in the following sections is provided only for users who would like to do their own low-level programming.

## 4.2 I/O Port Address Map

PCI-1720U requires 12 addresses in the PC's I/O space. The address of each register is specified as an offset from the card's base address. For example, BASE  $\pm$  0 is the card's base address and BASE  $\pm$  7 is the base address plus seven bytes. Table 4.1 shows the function of each register and its address relative to the card's base address

| <i>Table 4.1:</i>            | PCI | -1720       | OU R | egiste      | er Fort | mat ai | nd F | unctio | n Description                       |     |

|------------------------------|-----|-------------|------|-------------|---------|--------|------|--------|-------------------------------------|-----|

| Base<br>Address<br>+ Decimal | 7   | 6           | 5    | 4           | 3       | 2      | 1    | 0      | Function<br>Description             | R/W |

| +0                           | D7  | D6          | D5   | D4          | D3      | D2     | D1   | D0     | D/A output                          | W   |

| +1                           |     |             | •    |             | D11     | D10    | D9   | D8     | channel 0                           |     |

| +2                           | D7  | D6          | D5   | D4          | D3      | D2     | D1   | D0     | D/A output                          | W   |

| +3                           |     |             | •    |             | D11     | D10    | D9   | D8     | channel 1                           |     |

| +4                           | D7  | D6          | D5   | D4          | D3      | D2     | D1   | D0     | D/A output                          | W   |

| +5                           |     |             |      |             | D11     | D10    | D9   | D8     | channel 2                           |     |

| +6                           | D7  | D6          | D5   | D4          | D3      | D2     | D1   | D0     | D/A output                          | W   |

| +7                           |     |             | 1    |             | D11     | D10    | D9   | D8     | channel 3                           |     |

| +8                           |     |             |      |             |         |        |      |        | D/A voltage range and polarity      | R/W |

| +9                           |     | ll.         |      | ll.         |         | il.    |      |        | Synchronized output prompt register | W   |

| +15                          |     |             |      |             |         |        |      | SC0    | Synchronized output control bit     | R/W |

| +20                          |     | =<br>=<br>= |      | =<br>=<br>= | D3      | D2     | D1   | D0     | BoardID Regis-<br>ter               | R   |

<sup>\* &</sup>quot;R" means readable and "W" means writable

## 4.2.1 D/A Output Channel 0 to 3

The write-only registers of BASE + 2(n) and BASE + (2(n) + 1) accept data for D/A output channel n (n = 0, 1, 2, 3)

| <i>Table 4.2:</i>    | 4.2: Register for D/A Data |    |    |    |                         |     |    |    |                      |   |

|----------------------|----------------------------|----|----|----|-------------------------|-----|----|----|----------------------|---|

| Base                 |                            |    |    |    | Function<br>Description | R/W |    |    |                      |   |

| Address<br>+ decimal | 7                          | 6  | 5  | 4  | 3                       | 2   | 1  | 0  | Description          |   |

| +2(n)                | D7                         | D6 | D5 | D4 | D3                      | D2  | D1 | D0 | D/A output channel n | W |

| +(2(n)+1)            |                            |    | •  |    | D11                     | D10 | D9 | D8 | CHAIRIETT            |   |

**D11** ~ **D0** Digital to Analog data. D0 is the LSB (Least Significant Bit) and D11 is the MSB (Most Significant Bit) of the D/A data.

Note! To write D/A data, write the low byte first, then write the high byte.

## 4.2.2 D/A Voltage Range and Polarity

The read-writable register of BASE + 8 allows users to set the D/A voltage range and polarity.)

| Table 4.3: Register for D/A Voltage Range and Polarity |             |              |             |              |             |              |             |              |                                      |     |

|--------------------------------------------------------|-------------|--------------|-------------|--------------|-------------|--------------|-------------|--------------|--------------------------------------|-----|

| Base                                                   |             | Data         |             |              |             |              |             |              |                                      | R/W |

| Address + decimal                                      | 7           | 6            | 5           | 4            | 3           | 2            | 1           | 0            | Description                          |     |

| +8                                                     | DA3_<br>U/B | DA3_<br>5/10 | DA2_<br>U/B | DA2_<br>5/10 | DA1_<br>U/B | DA1_<br>5/10 | DA0<br>_U/B | DA0_<br>5/10 | D/A voltage<br>range and<br>polarity | R/W |

| Table 4.4: Output Range of D/A Channel n |           |                            |  |  |  |  |  |  |

|------------------------------------------|-----------|----------------------------|--|--|--|--|--|--|

| D An_U/B                                 | D An_5/10 | D/A channel n output range |  |  |  |  |  |  |

| 0                                        | 0         | 0 to +5 V                  |  |  |  |  |  |  |

| 0                                        | 1         | 0 to +10 V                 |  |  |  |  |  |  |

| 1                                        | 0         | -5 to +5 V                 |  |  |  |  |  |  |

| 1                                        | 1         | -10 to +10 V               |  |  |  |  |  |  |

<sup>\*</sup> n = 0,1,2,3.

## 4.2.3 Synchronized Output Prompt Register

During normal operation, the PCI-1720U will accept digital values one at a time from the host PC, convert these values to analog values, and immediately output these analog values from the channels directed by the host PC.

However, the PCI-1720U has the capability to store each analog value in its proper channel buffer as it is generated, then simultaneously output one analog value from each of its four channels on receipt of a synchronizing character. Any character can act as a synchronizing character, but it must be written to the BASE + 9 register to prompt synchronized output.

## 4.2.4 Synchronized Output Control Bitt

| <i>Table 4.5:</i>    | Table 4.5: Synchronized Output Control Bit |   |   |   |      |   |                   |     |                                 |     |

|----------------------|--------------------------------------------|---|---|---|------|---|-------------------|-----|---------------------------------|-----|

| Base                 |                                            |   |   |   | Data |   | Function Descrip- | R/W |                                 |     |

| Address<br>+ decimal | 7                                          | 6 | 5 | 4 | 3    | 2 | 1                 | 0   | tion                            |     |

| +15                  |                                            |   |   |   |      |   |                   | SC0 | Synchronized output control bit | R/W |

The register BASE  $\pm$  15 stores the synchronized output control bit. When the SC0 bit is set to 1, the synchronized data output function is enabled and analog values will not be output until a character is written to the BASE  $\pm$  9 register. When the SC0 bit is set to 0, the synchronized data output function is disabled. Analog data output occurs as soon as an output channel receives an element of output data.

## 4.3 Unipolar and Bipolar Binary Code Tables

| Table 4. | Table 4.6: Unipolar Binary Code Table |      |                                   |  |  |  |  |  |  |  |  |

|----------|---------------------------------------|------|-----------------------------------|--|--|--|--|--|--|--|--|

| Dig      | ital Input (                          | Code | Examples of Analog Output Voltage |  |  |  |  |  |  |  |  |

| MSB      |                                       | LSB  |                                   |  |  |  |  |  |  |  |  |

| 1111     | 1111                                  | 1111 | Vref (4095/4096)                  |  |  |  |  |  |  |  |  |

| 1000     | 0000                                  | 0001 | Vref (2049/4096)                  |  |  |  |  |  |  |  |  |

| 1000     | 0000                                  | 0000 | Vref (2048/4096)                  |  |  |  |  |  |  |  |  |

| 0111     | 1111                                  | 1111 | Vref (2048/4096)                  |  |  |  |  |  |  |  |  |

| 0000     | 0000                                  | 0001 | Vref (1/4096)                     |  |  |  |  |  |  |  |  |

| 0000     | 0000                                  | 0000 | Vref (0/4096)                     |  |  |  |  |  |  |  |  |

- Notes: 1. Vref is the reference source voltage that you selected. Vref is +5 V or +10 V.

- 2. Nominal full scale is given by FS = Vref ( (4095/4096).

- 3. Nominal LSB magnitude is given by LSB = Vref ((1/4096).

| Table 4.7: Bipolar Binary Code Table |      |      |                                   |

|--------------------------------------|------|------|-----------------------------------|

| Digital Input Code                   |      |      | Examples of Analog Output Voltage |

| MSB                                  |      | LSB  |                                   |

| 1111                                 | 1111 | 1111 | Vref (2047/2048)                  |

| 1000                                 | 0000 | 0001 | Vref (1/2048)                     |

| 1000                                 | 0000 | 0000 | 0                                 |

| 0111                                 | 1111 | 1111 | -Vref (1/2048)                    |

| 0000                                 | 0000 | 0001 | -Vref (2047/2048)                 |

| 0000                                 | 0000 | 0000 | -Vref (2048/2048)                 |

Notes:

- 1. Vref is the reference source voltage that you selected. Vref is +5 V or +10 V.

- 2. Nominal full scale is given by FS = Vref ((2047/2048)).

- 3. Nominal LSB magnitude is given by LSB = Vref ((1/2048).

# **Signal Connections**

## **Chapter 5 Signal Connections**

### 5.1 Overview

Making correct signal corrections is important for accurate data transmissions. Since most data acquisition applications involve some form of voltage measurement, making a sound signal connection will also protect your equipment against possible damage. This chapter shows you how to make proper signal connections to use PCI-1720U.

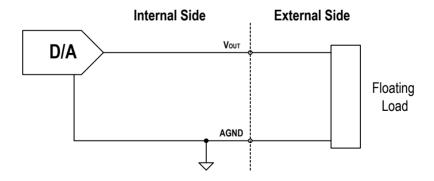

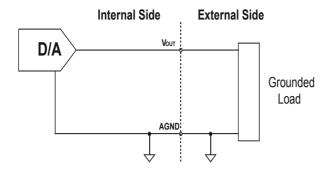

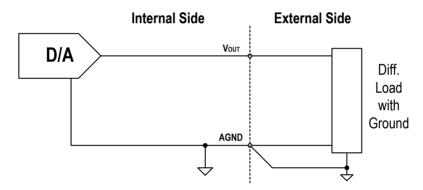

## 5.2 D/A Voltage Output Connections

PCI-1720U supports four channels of D/A voltage output. Only one output signal wire is used with each channel. The voltage output is referenced to a common ground (AGND).

There are three types of voltage output connections:

- 1. Floating load.

- 2. Grounded load.

- 3. Differential load with ground.

They are shown in the following illustrations.

Figure 5.1: Floating-load Connection for D/A Voltage Output

Figure 5.2: Grounded-load Connection for D/A Voltage Output

Figure 5.3: Differential-load Connection for D/A Voltage Output

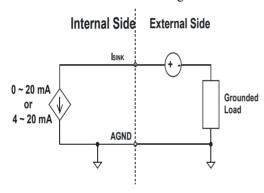

#### 5.3 Current Sink Connections

The PCI-1720U's current loop output uses a 0 to +5 V (unipolar) voltage output as each channel's driving source. Current drive circuits consist of a power field-effect transistor (FET). The current output's voltage bias must be less then 50 V for accurate results. The card also provides an internal +12 V power source for current loop excitation.

You can use three types of current sink connections:

- 1. Grounded load with a floating power supply.

- 2. Floating load with a grounded power supply.

- 3. Floating load with an internal +12 V power supply.

These are shown in the following illustrations.

Figure 5.4: Grounded-load connection with a floating power supply

Figure 5.5: Floating-load connection with a grounded power supply

Figure 5.6: Floating-load Conn. with an Internal +12 VDC Power Supply

## 5.4 Current Sink Load and Power Supply

You have to select the current sink load and power supply carefully. The current sink circuitry of the PCI-1720U is as shown below.

Figure 5.7: PCI-1720U Current Sink Circuitry

#### where

VS: Power supply voltage of current sink.

RL: Load of current sink.

PD: Power dissipation of FET.

When you determine VS and RL, three conditions must be satisfied.

$$VS > (RL + 249) (0.02)$$

VS £ 50

$$PD = (VS - (RL + 249) \times 0.02) \times 0.02 < 0.2$$

## Example 1

If you use the internal power supply VS = +12 V, RL must be less than 351 W (12 / 0.02 - 249 > RL). Select RL = 200 W, PD = 0.0604 < 0.2 OK!

## Example 2

If you use the external power supply VS = +40 V, RL must be less than 1.75 kW (40 / 0.02 - 249 > RL).

Select RL = 200 W, PD = 0.62 > 0.2 fail!

Reselect RL = 1 kW, PD = 0.3 > 0.2 fail!

Reselect RL = 1.5 kW, PD = 0.1 < 0.2 OK!

# **Calibration**

## Appendix A Calibration

## A.1 Overview

The PCI-1720U card uses eight variable resistors (VRs), two for each channel, which allow you to calibrate each of the card's four output channels. The following information outlines the function of each VR. Refer to the illustration shown below for the locations of the PCI-1720U's VRs.

Figure A.1: PCI-1720U VR assignment

- VR1 Channel 0's full scale (gain) adjustment.

- VR2 Channel 1's full scale (gain) adjustment.

- VR3 Channel 2's full scale (gain) adjustment.

- VR4 Channel 3's full scale (gain) adjustment.

- VR5 Channel 0's offset adjustment.

- VR6 Channel 1's offset adjustment.

- VR7 Channel 2's offset adjustment.

- VR8 Channel 3's offset adjustment.

You should use a precision voltmeter/ammeter to obtain accurate readings when calibrating the PCI-1720U. Standard procedures for performing a calibration are given below.

## A.2 Unipolar Output Calibration

- 1. Select an appropriate output range for the channel to be calibrated.

- 2. Set all digital input codes to 0. Then adjust VRn (n = 5, 6, 7, 8 depending on what channel is to be calibrated, see prior page) until your voltmeter's reading is 0.000 volts.

- 3. Set all digital input codes to 1 (see Unipolar Binary Code Table in Section 4.3). Now, adjust VRn (n = 1, 2, 3, 4 depending on what channel is to be calibrated, see prior page) until your voltmeter shows a reading equal to the output voltage shown in the Unipolar Binary Code Table in Section 4.3.

- 4. Repeat steps 2 and 3 until both of them are satisfied.

## A.3 Bipolar Output Calibration

- 1. Select an appropriate output range for the channel to be calibrated.

- 2. Set all digital input codes to 100000000000. Adjust VRn (n = 5, 6, 7, 8 depending on what channel is to be calibrated, see prior page) until your voltmeter's reading is 0.000 volts.

- 3. Set all digital input codes to 1 (see Bipolar Binary Code Table in Section 4.3). Now, adjust VRn (n = 1, 2, 3, 4 depending on what channel is to be calibrated, see prior page) until your voltmeter shows a reading equal to the output voltage shown in the Bipolar Binary Code Table in Section 4.3.

- 4. Repeat steps 2 and 3 until both of them are satisfied.

## A.4 Current Sink Calibration

- 1. Select the  $0 \sim +5$  V (unipolar) output range for the channel to be calibrated.

- 2. Set all digital input codes to 0. Then adjust VRn (n = 5, 6, 7, 8 depending on what channel is to be calibrated, see prior page) until your ammeter's reading is 0.00 mA or 4.00 mA (Depending on jumper setting JP1 to JP4, see Section 3.1.1).

- 3. Set all digital input codes to 1. Now, adjust VRn (n = 1, 2, 3, 4 depending on what channel is to be calibrated, see prior page) until your ammeter shows a reading equal to 20.00 mA.

- 4. Repeat steps 2 and 3 until both of them are satisfied.